高速PCB设计:信号与电源完整性工程师(Sigrity/HFSS仿真专家)简历模板

本模板专为信号与电源完整性工程师(SI/PI Eng.)量身定制,重点突出高速PCB设计中的Sigrity/HFSS仿真技能,如眼图(Eye Diagram)分析、DDR5/PCIe5.0串扰与衰减优化报告。模板结构清晰,强调项目经验和技术细节,助力您在竞争激烈的科技行业中脱颖而出,获得理想职位。

模板亮点

- 突出Sigrity/HFSS等专业仿真工具应用

- 强调DDR5/PCIe5.0等高速接口设计经验

- 专业展示眼图分析、串扰与衰减优化成果

- 结构化项目经验展示,量化技术贡献

- 适配高速PCB设计与信号完整性领域

相关标签

适用人群

本模板特别适合信号与电源完整性工程师岗位的求职者使用,具备3-5年经验工作经验的专业人士, 通过技术类风格的设计,帮助您在科技行业 行业中脱颖而出,展现专业形象和核心竞争力。

使用模版创建简历相关模板

同样优秀的技术类风格模板

高效客户端开发工程师简历模板(iOS/Android双平台优化)

本简历模板专为iOS和Android客户端开发工程师设计,强调技术深度与项目经验。模板结构清晰,突出开发技能、项目亮点和技术栈,帮助求职者快速吸引招聘官注意,尤其适合有iOS或Android双平台开发经验的工程师。简洁专业的版面布局,确保信息传达高效。

推荐算法工程师高薪简历模板:斩获大厂offer,突出项目经验与数据能力

本简历模板专为推荐算法工程师量身定制,突出项目经验、模型优化能力和数据分析洞察力。通过清晰的结构和重点内容展示,帮助求职者在众多简历中脱颖而出,直击HR和面试官的关注点,提高面试邀约率。适用于1-5年推荐算法经验的求职者。

数字IC设计工程师专业简历模板:高效展现芯片设计实力

本模板专为数字IC设计工程师量身打造,突出您的芯片设计、验证、综合与布局布线等核心技能。结构清晰,重点突出项目经验与技术成果,助您在众多求职者中脱颖而出,快速获得心仪的数字IC设计职位面试机会。

跨领域求职优选:云计算工程师专业简历模板

本简历模板专为有志于转行或跨领域发展为云计算工程师的人士设计。模板突出项目经验、技术栈和学习能力,强调可迁移技能,帮助您在激烈的竞争中脱颖而出,成功转型云计算领域。简洁高效的布局,让招聘经理快速捕捉您的核心优势。

新能源汽车控制系统工程师简历模板:专业、高效、助力职业腾飞

本简历模板专为车辆控制系统工程师量身定制,尤其适用于新能源汽车领域的专业人才。模板设计简洁大气,内容结构清晰,突出项目经验、技术专长和解决问题能力。无论是资深工程师寻求职业突破,还是有志于进入新能源汽车行业的求职者,都能通过此模板高效展示核心竞争力,助力您在激烈的市场竞争中脱颖而出。

NLP驱动智能体工程师简历模板:对话式AI Agent构建专家

本简历模板专为NLP驱动智能体工程师设计,突出在对话式AI Agent构建方面的专业能力和项目经验。模板结构清晰,重点强调自然语言处理技术、大模型应用、多模态交互以及Agent框架搭建等核心技能,助力求职者快速获得面试机会。

游戏客户端开发工程师简历模板 (U3D/UE)

本简历模板专为游戏客户端开发工程师量身定制,尤其适合熟悉Unity3D或Unreal Engine的专业人士。模板设计注重突出技术能力、项目经验和游戏开发成果,结构清晰,排版专业,旨在帮助求职者快速吸引招聘官的注意,展现其在游戏开发领域的核心竞争力。无论是资深开发者还是经验丰富的工程师,都能通过此模板有效展示其专业技能和项目贡献。

LLM大模型算法工程师简历模板:突出AI技术与项目经验

本模板专为大模型算法工程师设计,强调AI技术深度、LLM项目经验和算法优化能力。布局清晰,逻辑严谨,突出量化成果,助力AI领域专业人士脱颖而出。适用于有志于在大模型、深度学习、自然语言处理等前沿领域发展的算法工程师。

简历写作

专业指导,提升简历质量

诺尔威测量设备上海2026春招:物理机械专业投递指南与薪资分析

诺尔威测量设备上海2026春招开启,面向物理、机械专业提供技术应用岗。本文解读外企背景、岗位稳定性及“薪资面议”背后的求职注意点,助你快速判断是否值得投递。

广州市白云区教育局2026春招:不限专业报考指南

解读广州市白云区教育局2026年春招公告,分析“不限专业、不限学历”背后的竞争逻辑。明确事业单位编制性质,帮助应届生判断岗位匹配度,避开陪跑陷阱,精准准备入编考试。

新疆维药2026暑期实习:8省招聘真相与转正机会解读

新疆维药2026暑期实习开放8省招聘,表现优异可转正。本文拆解其民族药企背景、营销储备生岗位要求及跨省布局背后的职业机会,帮应届生判断是否值得投递。

阿里灵犀互娱2026暑期实习:美术生进大厂,只招写实风?

阿里灵犀互娱2026暑期实习仅开放角色与场景原画两个写实风格岗位。背靠阿里生态资金稳定,但风格要求极度垂直。适合擅长“写实冷兵器”与“东方神话”题材的美术生,非写实风格求职者需谨慎投递。

黑龙江省气象部门2026春招:不限专业能进体制?大兴安岭岗值不值得冲

黑龙江省气象部门2026春招启动,岗位集中在大兴安岭地区,学历专业双不限。本文深度解读该“铁饭碗”岗位的稳定性、隐性福利及地域限制,帮你判断是捡漏机会还是偏远深坑。

苏州观瑞汽车2026暑期实习:硕士专属,重科研实测

苏州观瑞汽车2026暑期实习仅面向硕士,由教授级专家领衔。适合想在自动驾驶领域积累实测数据、产出专利论文的求职者。初创团队资源倾斜度高,非工业化量产路线。

模板内容

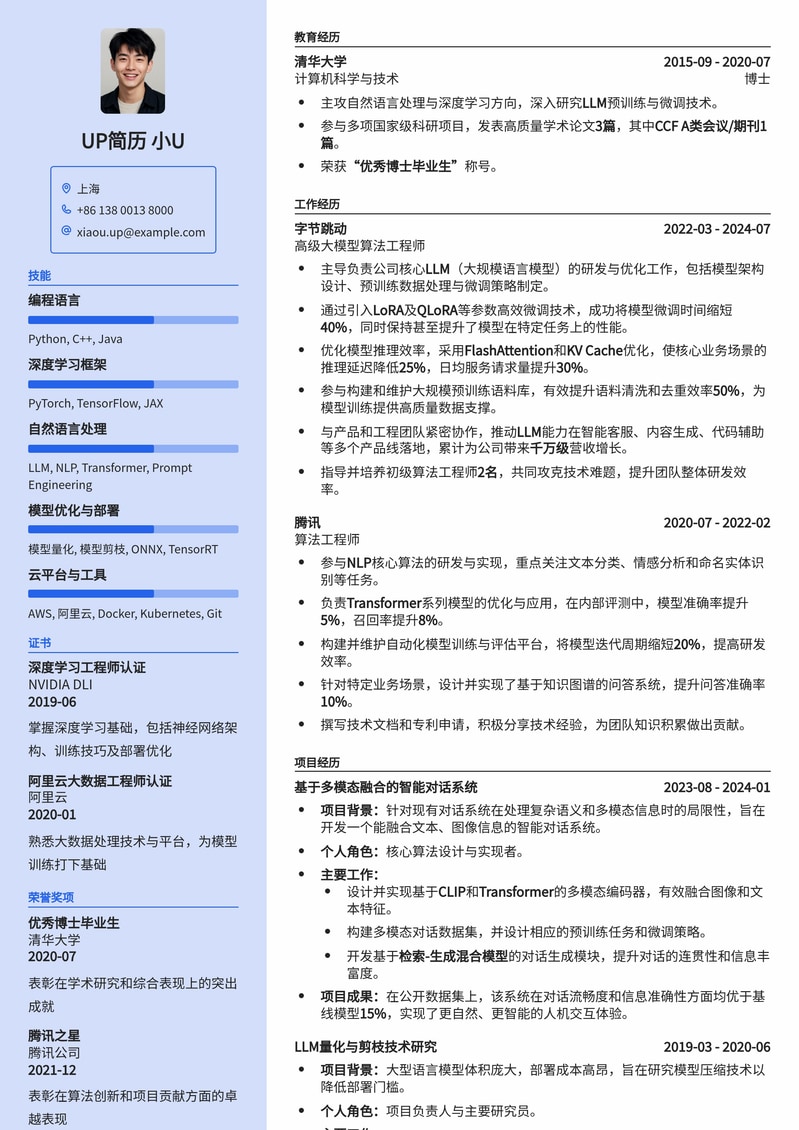

UP简历 小U

个人总结

资深信号与电源完整性工程师,在高速PCB设计、仿真与优化领域拥有<strong>5年</strong>以上经验。精通<strong>Sigrity</strong>、<strong>HFSS</strong>等仿真工具,专注于<strong>DDR5</strong>和<strong>PCIe5.0</strong>等高速接口的<strong>眼图分析</strong>、<strong>串扰与衰减优化</strong>,具备独立完成复杂<strong>SI/PI报告</strong>的能力。致力于通过专业技能确保产品高性能与可靠性,驱动技术创新与效率提升。

工作经历

高级信号与电源完整性工程师

华为技术有限公司

- 主导5G基站核心板和数据中心服务器主板的高速PCB信号完整性(SI)和电源完整性(PI)分析与优化工作,成功支持3款旗舰产品按时量产。

- 运用ANSYS SIwave和HFSS对DDR5、PCIe5.0等高速接口进行全链路仿真与验证,通过眼图(Eye Diagram)分析、TDR/TDT测量,将信道裕量提升15%,确保了25Gbps以上高速信号的稳定传输。

- 负责电源分配网络(PDN)设计与优化,通过Sigrity PowerSI进行去耦电容配置、平面谐振分析,将电源噪声纹波降低20%,满足芯片供电要求。

- 针对复杂高速互联场景,成功解决串扰(Crosstalk)、反射(Reflection)、损耗(Loss)等关键问题,提出并实施过孔优化、差分线对等长、阻抗控制等10余项设计改进措施,有效提升系统整体性能。

- 独立撰写并提交高速PCB SI/PI仿真报告超过50份,为硬件设计团队提供详尽的优化建议和风险评估,推动设计迭代效率提升10%。

- 参与制定公司内部高速设计规范与仿真流程,并对新入职工程师进行专业培训,提升团队整体SI/PI能力。

信号完整性工程师

中兴通讯股份有限公司

- 参与通信设备背板和交换机主板的高速信号完整性分析,协助解决设计阶段的SI问题,保障项目顺利推进。

- 熟练使用Cadence Allegro Sigrity进行前仿真(Pre-layout)和后仿真(Post-layout),对DDR4、PCIe Gen4等接口进行参数提取和信道仿真。

- 负责串扰(Crosstalk)分析与抑制,通过优化走线间距、引入屏蔽线等方法,有效降低了信号串扰8%。

- 协助进行电源完整性初步分析,评估PDN去耦方案,确保电压跌落符合标准。

- 与硬件设计工程师紧密合作,提供PCB堆叠、走线拓扑等方面的SI/PI设计指导,减少设计返工率5%。

- 积累了丰富的高速PCB设计评审经验,识别并规避潜在的信号完整性风险。

项目经历

DDR5高速内存接口SI/PI协同优化项目

华为技术有限公司 (内部项目)

- 项目背景:为满足下一代服务器对内存带宽和容量的严苛要求,需设计并优化支持DDR5-4800Mbps的高速内存接口,面临极高的信号衰减和噪声挑战。

- 个人职责:核心SI/PI工程师,负责DDR5通道的完整SI/PI仿真与优化。

- 行动与贡献:

- 利用Sigrity PowerSI和HFSS进行DDR5信道建模,对DQ、DQS、CMD/ADDR信号进行眼图分析,识别并量化了关键信号的串扰、反射和损耗效应。

- 创新性地提出并实施了多层PCB堆叠优化方案,通过调整介质常数、铜箔厚度及过孔结构,有效降低了传输损耗12%,并改善了阻抗匹配。

- 针对DDR5 PDN,通过精密计算去耦电容网络,结合PowerSI进行AC/DC仿真,将电源噪声峰峰值控制在±30mV以内,确保内存控制器稳定工作。

- 与内存控制器厂商、PCB供应商紧密合作,推动设计方案的落地,并指导实验室进行S参数测试验证,测试结果与仿真结果吻合度高达90%。

- 项目成果:成功设计出满足DDR5-4800Mbps速率要求的内存接口,通过严苛的眼图裕量测试,系统误码率(BER)达到10^-12级别,为新一代服务器产品的上市提供了关键技术支持,预计每年可节省研发成本[XX]万元。

PCIe5.0高速串行总线信道优化项目

中兴通讯股份有限公司 (内部项目)

- 项目背景:面对PCIe5.0 32GT/s超高数据速率带来的信号完整性挑战,需要对高速串行总线信道进行全面优化,以满足产品性能要求。

- 个人职责:SI工程师,负责PCIe5.0差分对的信道仿真与优化。

- 行动与贡献:

- 使用ANSYS HFSS对PCIe5.0连接器、过孔、传输线进行三维电磁场仿真,提取精确的S参数模型。

- 利用Sigrity SystemSI进行端到端信道仿真,重点分析插入损耗(Insertion Loss)、回波损耗(Return Loss)以及近端串扰(NEXT)、远端串扰(FEXT)对眼图的影响。

- 设计并验证了多级均衡器(EQ)策略,包括发送端预加重(Pre-emphasis)和接收端判决反馈均衡(DFE),有效补偿了信道损耗,使眼图高度和宽度分别提升了15%和10%。

- 针对高速信号的Skew问题,通过优化差分对走线布局,将Skew控制在5ps以内,显著提升了信号时序裕量。

- 撰写详细的PCIe5.0信道优化报告,为硬件设计团队提供了具体的设计指导和验证方案,确保了PCIe5.0接口的稳定性和可靠性。

- 项目成果:成功优化PCIe5.0高速串行总线信道,通过了严格的PCI-SIG一致性测试,将误码率降低了一个数量级,支持了新一代网络处理器芯片的集成,为公司产品性能带来显著提升。

教育背景

上海交通大学

硕士 · 电子科学与技术

华中科技大学

学士 · 电子信息工程

- 主修课程:电磁场与电磁波、微波技术、高速电路设计、信号完整性原理。

- 硕士论文:《基于先进封装技术的高速互联信号完整性研究》,深入分析了多层PCB和封装中的信号传输特性。

- 荣获优秀毕业生称号,并多次获得学业奖学金。

- 核心课程:电路原理、模拟电子技术、数字电子技术、通信原理、高频电子线路。

- 参与“智能家居系统”创新项目,负责传感器数据采集模块设计与调试。

- 获得国家励志奖学金,培养了扎实的电子工程基础。

技能专长

信号完整性仿真

Sigrity PowerSI · Sigrity SystemSI · ANSYS HFSS · ADS · Spice

电源完整性分析

PDN设计与优化 · 去耦电容配置 · 平面谐振分析 · IR Drop分析

高速接口设计

DDR5 · PCIe5.0 · SerDes · Ethernet · MIPI

测试与验证

眼图分析 · TDR/TDT · S参数测量 · 示波器 · 矢量网络分析仪

PCB设计与评估

Allegro Layout · PCB堆叠设计 · 阻抗控制 · 过孔优化 · EMC/EMI

证书资质

Cadence Allegro Sigrity SI/PI Expert Certification

Cadence Design Systems

证明在Cadence Sigrity工具进行信号与电源完整性分析的专业能力。

ANSYS HFSS Advanced User Certificate

ANSYS, Inc.

认证在ANSYS HFSS进行三维电磁场仿真和高速互联分析的熟练技能。

获奖经历

公司年度优秀员工

华为技术有限公司

表彰在高速PCB SI/PI设计与优化工作中做出的突出贡献,有效保障了多个关键项目的顺利交付。

技术创新奖

华为技术有限公司

奖励在DDR5内存接口信号完整性优化方面提出的创新性解决方案,显著提升了产品性能。

优秀毕业生

上海交通大学

表彰在学业成绩、科研能力及综合素质方面的卓越表现。

开始使用高速PCB设计:信号与电源完整性工程师(Sigrity/HFSS仿真专家)简历模板模板

选择专业模板,AI智能填写,3分钟完成简历制作